半導体における微細化とは?技術のポイントを解説

現代社会において、スマートフォン、PC、自動車、AIなど、あらゆるデジタルデバイスやシステムの中核を担うのが半導体です。その性能向上の原動力となってきたのが、「微細化」と呼ばれる技術革新です。

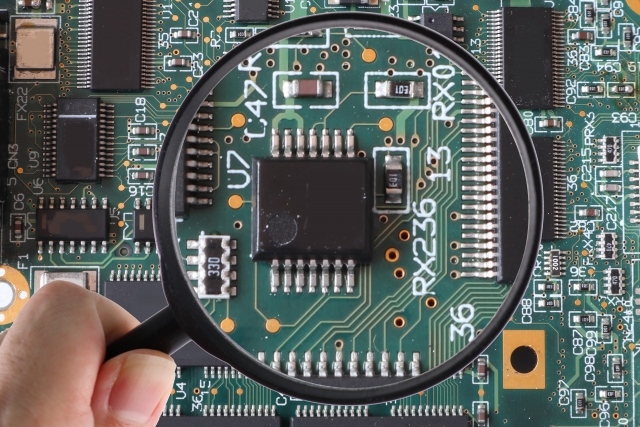

半導体チップ上の回路の線幅を極限まで狭めることで、限られた面積により多くのトランジスタを集積し、処理能力の向上と消費電力の削減を実現してきました。この微細化は、ナノメートル(nm)という原子数個分に迫る極めて小さなスケールで行われ、「ナノテクノロジー」の粋を集めた精密製造技術の結晶と言えます。

長きにわたり半導体産業を牽引してきたのは、「半導体集積回路のトランジスタ数が約2年ごとに倍増する」というムーアの法則でした。この法則は、単なる予測を超え、業界全体の技術開発や設備投資の指針となり、半導体メーカーが技術革新を追求する強力なモチベーションとなってきました。

本記事では、この半導体における微細化がなぜ重要なのか、そしてそれを支える基盤技術であるナノメートル単位の精密加工、ムーアの法則の歴史的意義、さらには微細化の限界とそれを乗り越えるための新たな技術動向について、詳しく解説していきます。デジタル社会の進化を支える半導体微細化の奥深さに迫りましょう。

半導体における微細化の重要性

半導体回路における線幅を極限まで狭め、それによって半導体チップのサイズを飛躍的に小型化する「微細化」は、現代の大規模集積回路(LSI)を実現する上で不可欠な技術であり、その鍵を握っています。

この微細加工技術は、今日に至るまで半導体業界の技術革新と発展を牽引し続けている、まさに中核をなす存在です。

微細化で重要な単位ナノメートルとは?

長さの単位である「ナノメートル(nm)」は、非常に微細な世界を表します。これは1マイクロメートル(µm)の1000分の1、そして1ミリメートル(mm)の100万分の1に相当します。

このようなナノメートルクラスの極めて微小な単位を扱う技術全般は、「ナノテクノロジー」と呼ばれ、半導体製造はその最たる例の一つです。

微細化を支えるムーアの法則

半導体製造における技術トレンド、特に「微細化」の進展を長きにわたり支えてきたのが「ムーアの法則」(Moore’s Law)です。これは物理学的な法則ではなく、アメリカの大手半導体メーカーであるIntel(インテル)の共同創業者、ゴードン・ムーア氏が1965年に提唱した、半導体製造に関する長期的な予測に当たります。

この法則の基本的な内容は、「半導体集積回路に搭載されるトランジスタの数(すなわち集積度)は、およそ2年ごとに倍増する」というものです。1965年の論文で初めて示され、1975年に現在の形に修正されて以来、半導体業界全体に広く認知される長期的なトレンドとなりました。多くの半導体メーカーは、この予測を製造技術開発や設備投資の重要な指標として活用し、その実現に向けて努力を重ねてきました。

微細化を実現する微細加工技術は、特に半導体製造の前工程において極めて重要です。この技術を用いることで、回路パターンの寸法を縮小し、回路の線幅を微細化していくことが可能になります。今日の最先端半導体分野では、回路パターンの最小寸法は10nm(1mmの10万分の1)以下まで縮小されており、これは原子数個分のオーダーに迫る精密さです。

微細化における今後の展望

しかし、微細化の進展に伴い、新たな課題も顕在化してきました。集積された数百億個を超える膨大な数のトランジスタにおいて、その電気的特性のばらつきが無視できなくなる問題や、回路に電気が流れる際に発生するごくわずかな電流の漏れ(リーク電流)の影響などが顕著になってきたのです。また、製造コストが飛躍的に増加する一方で、それに見合うだけの性能向上が難しくなり、さらには加工技術における物理的な限界も視野に入ってきています。

このような状況に対応するため、半導体業界ではさまざまな取り組みが進められています。例えば、トランジスタの構造そのものを見直す「FinFET(フィンフェット)」や、より新しい「GAA(Gate-All-Around)」などの技術開発、あるいは複数の異なる機能を持つチップを1つのパッケージにまとめて収納する「異種チップ積層」といった技術が実用化されつつあります。これらのアプローチは、ムーアの法則が示す集積度向上を、従来の微細化一辺倒ではなく、新たな工夫や多角的な技術革新を加える形で進化させていると言えるでしょう。

半導体の微細化を支える要素

半導体の微細化は、いくつかの要素によって支えられています。ここでは、代表的なポイントを3つ紹介します。

2つの素子を分離し干渉させない

半導体デバイスを構成する個々の「素子」を形成する工程は、高度に複雑かつ精密な一連の基本プロセスから成り立っています。これには、洗浄(異物除去)、成膜(薄膜の形成)、リソグラフィ(回路パターンの転写)、エッチング(不要な膜の除去)、イオン注入・熱処理(不純物ドーピングと活性化)、平坦化(表面の均一化)、そして検査(品質確認)といった工程が含まれます。

これらのプロセスは、目的の素子構造を作り込むために何度も繰り返し実行されます。特に大規模集積回路(LSI)においては、この工程で形成される個々のトランジスタの品質(良否)が、最終的なデバイス全体の性能に直接的に影響を与えるため、極めて重要な意味を持ちます。

CMOS構造における素子間分離の重要性

今日の最先端半導体分野では、主に「pチャネルトランジスタ(pMOS)」と「nチャネルトランジスタ(nMOS)」という異なる特性を持つ二種類のトランジスタを組み合わせた「CMOS(Complementary Metal-Oxide-Semiconductor)構造」が広く採用されています。

このCMOSプロセスでは、隣接して配置されるpMOSとnMOSの両方の素子が、互いに電気的に干渉し合わないようにすることが非常に重要です。この干渉を防ぐために、各トランジスタを形成する「活性領域」(電流が流れる部分)と厳密に区別し、その間に「素子間分離領域」を設ける技術が不可欠となります。

この素子間分離領域を製造する技術としては、現在「STI(Shallow Trench Isolation)」と呼ばれる分離技術が主流となっています。STIは、半導体ウェーハ表面に比較的浅い溝(トレンチ)を形成し、その溝に誘電体(通常は酸化シリコン)を埋め込むことで、物理的かつ電気的なバリアを作り出す方法です。

これにより、隣接するトランジスタ間の漏れ電流や電気的なクロストークを効果的に抑制し、デバイスの安定した動作と高性能化を実現しています。

イオン注入技術による不純物拡散と特性制御

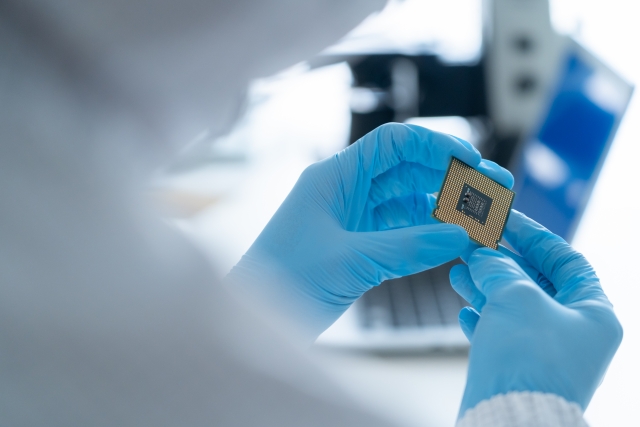

半導体の電気的特性を精密に制御するためには、「不純物」を正確な位置に、適切な量だけ添加する技術が不可欠です。この不純物の添加と拡散には、「イオン注入技術」が用いられます。例えば、半導体(シリコン)にp型の特性を与えるためには「ボロン(B)」、n型の特性を与えるためには「リン(P)」などの不純物原子をイオン化し、高いエネルギーでウェーハに打ち込みます。

イオン注入によって打ち込まれた不純物原子は、その後の熱処理(アニーリング)によって結晶格子中に電気的に活性化され、特定の領域がp型半導体またはn型半導体へと変化します。このプロセスにより、トランジスタのゲート、ソース、ドレインといった各部分の電気的特性が precisely 設計通りに形成され、半導体デバイスの機能が実現されるのです。

厳密な寸法管理が不可欠に

トランジスタの性能や信頼性を決定づける上で、ゲート形成は極めて重要な工程であり、その成功には厳密な寸法管理が欠かせません。この工程では、まずpMOS(pチャネルMOSトランジスタ)およびnMOS(nチャネルMOSトランジスタ)の活性領域の上に、トランジスタの心臓部となるゲート酸化膜(多くはシリコン酸化膜を主成分とするゲート絶縁膜)を極めて薄く形成します。その上に導電性材料であるポリシリコン膜を成膜し、これがゲート電極の土台となります。

次に、このポリシリコン膜の上に感光性の材料であるフォトレジストを塗布し、紫外線などの光を用いて微細なゲートパターンを転写します(リソグラフィ工程)。このパターンをマスクとして、その下のポリシリコン膜とゲート酸化膜に対して精密なエッチング(化学的または物理的な除去プロセス)を行い、正確な形状のゲートを形成します。エッチングが完了した後、不要になったレジストパターンは慎重に除去されます。

ゲートが形成された後は、同様のプロセスを用いて、pMOSおよびnMOSの各領域にソースとドレインと呼ばれる電極を作り込みます。ソースとドレインは機能的には電源の接続方向によって定義されますが、物理的な形状は互いに同じであり、対称的な構造を持っています。

高誘電率材料やメタルゲート電極を採用

半導体デバイスの微細化が極限まで進むにつれて、トランジスタのゲート絶縁膜の膜厚は原子数層レベルにまで薄くなりました。これに伴い、量子力学的なトンネル効果などによって、ゲートから意図しない電流が流れてしまうリーク電流の問題が顕著になりました。

このリーク電流を抑制し、デバイスの消費電力を低減するために、極薄のゲート絶縁膜には誘電率(材料が電荷を蓄える能力を示す物理量)が高い材料の採用が積極的に進められています。具体的には、従来のシリコン酸化膜の代わりに、ハフニウム系材料などの「高誘電率(High-k)材料」が用いられています。

同時に、ゲート絶縁膜の極薄化に伴い、従来のポリシリコンゲートでは「空乏層」(キャリアが不足する領域)が形成されやすくなり、これがデバイスの性能(特に電流駆動能力や閾値電圧の変動)に大きな影響を与えるようになりました。この問題を解決するため、より空乏化しにくく、抵抗の低い金属材料(メタル)をゲート電極に用いる「メタルゲート」へと技術が変化しています。これにより、トランジスタの性能向上と安定化が図られています。

これら3つの主要な電極(ゲート、ソース、ドレイン)の形成が完了した後は、その上部に層間絶縁膜を作製します。この絶縁膜には、各電極と外部配線層を電気的に接続するための微小な穴、すなわちコンタクトホールが精密に開けられます。

このコンタクトホールには、高い耐熱性や耐薬品性を持つ金属材料(主にタングステンが使われることが多いです)が埋め込まれ、電気的な経路が確立されます。これにより、トランジスタの3つの電極が、最終的にチップ全体を網羅する多層配線層と接続可能になり、複雑な回路機能が実現されるのです。

まとめ

本記事では、半導体における「微細化」が、いかに現代のデジタル社会を支える不可欠な技術であるかを詳しく見てきました。回路線幅をナノメートルレベルまで縮小し、チップに膨大な数のトランジスタを集積するこの技術は、ムーアの法則に導かれる形で性能向上と低消費電力化を追求し続けてきました。

微細化を支える根幹には、洗浄、成膜、リソグラフィ、エッチング、イオン注入、平坦化といった精密な製造プロセスがあり、特にトランジスタ間の電気的干渉を防ぐ「素子間分離(STI)」や、ゲート形成における「高誘電率材料」と「メタルゲート」の採用が、高性能化に大きく貢献しています。

しかし、物理的な限界や増大する製造コスト、リーク電流といった課題が顕在化し、従来の微細化だけでは性能向上が困難になりつつあります。この状況に対し、半導体業界は「FinFET」や「GAA」といった新たなトランジスタ構造の開発、さらには複数のチップを統合する「異種チップ積層」といった革新的なアプローチを推進しています。

これらの技術は、ムーアの法則が示す集積度向上の精神を受け継ぎながらも、その実現方法を多様化し、新たな次元へと進化させています。半導体技術は、これからも私たちの社会の進化を牽引し続けるでしょう。