FinFETとGAAで進化する次世代の半導体

半導体産業の進化を支えてきた微細化技術は、従来のプレーナ型トランジスタから立体構造へと大きく舵を切り、FinFETやGAAといった革新的な構造の採用が進んでいます。こうした構造の変化は、短チャネル効果やリーク電流といった微細化に伴う物理的な限界を克服するためのものです。現在では3nm世代にGAA構造が本格導入され、さらにその先にはCFETと呼ばれる次世代構造が見据えられています。

本記事では、FinFETからGAA、そしてCFETに至るまでの最先端トランジスタ技術の進展と、その背後にある課題や展望について解説します。

FinFETの導入とその技術的背景

トランジスタの微細化が限界に近づく中で、従来のプレーナ型構造では短チャネル効果などの物理的問題が顕在化してきました。これを克服するため、2011年に米Intelが22nmプロセスにおいてFinFET構造を実用化しました。FinFETは立体的なチャネル設計により、電流の制御性を飛躍的に向上させる技術です。このセクションでは、FinFETの構造的特長や製造に必要なプロセス技術について詳しく解説します。

FinFETとは

FinFET(Fin Field-Effect Transistor)は、従来のプレーナ型トランジスタが抱えていた微細化限界を突破するために開発された立体構造のトランジスタです。2011年、米Intelが22nmプロセスで初めて量産導入し、以降、多くの半導体メーカーが標準構造として採用しています。

FinFETの最大の特徴は、ソースとドレインの間に立てられたフィン(ひれ状構造)をチャネルとし、その三方向以上をゲート電極で囲むことにあります。この立体的な接触により、ゲートがチャネルをより強く制御できるようになり、リーク電流の低減やスイッチング速度の向上といった性能改善が可能となりました。

さらに、フィンの高さや間隔、幅を細かく調整することで、トランジスタの電気的特性を精密に制御できる柔軟性が得られる点もFinFETの利点です。これにより、短チャネル効果の抑制はもちろん、高速動作と低消費電力を両立させたプロセッサ設計が実現でき、スマートフォンやサーバーなど幅広い分野の高性能化を支える基盤技術となっています。

フィン形成のためのダブルパターニング技術

FinFET構造では、チャネル部となるフィンを微細かつ高アスペクト比で精密に形成する必要があります。ところが、従来の193nm ArF液浸露光技術では、22nm世代以降に求められる極端な線幅・間隔のパターンを一度の露光では生成できません。そこで用いられるのが「ダブルパターニング技術(Double Patterning Technology、DPT)」です。

この手法は、一つのパターンを複数回の露光とエッチング工程に分割することで、解像限界を超える高密度配線を実現します。たとえば、1回目の露光で奇数番目のフィンを、2回目で偶数番目のフィンを形成することで、半ピッチを大幅に縮めることができます。

しかし、このアプローチには課題もあります。露光マスクの枚数やエッチング回数が増えることで、工程数が増加し、製造コストが高騰します。また、各工程での位置ずれ(アライメント誤差)やエッチング精度のばらつきが歩留まりに直結するため、プロセス管理の高度化が求められます。こうした制約を克服するため、将来的にはEUV(極端紫外線)露光の本格導入が期待されていますが、現時点ではダブルパターニングが微細化を支える現実的なソリューションとして重要な役割を担っています。

GAA構造への移行と今後の展望

FinFETの限界が見え始めたなかで、さらなる微細化と性能向上を実現する次の一手として注目されたのがGAA(Gate-All-Around)構造です。この技術ではチャネルを完全にゲートで包み込むことで、リーク電流の抑制とスイッチング特性の向上が可能となります。ここではGAA構造の基本原理、量産への導入状況、そして次世代技術CFETへの展開まで、最先端のトランジスタ構造の進化について紹介します。

GAAはゲートを全方向から包み込む構造のこと

FinFETではゲートがチャネルの三方向から電流を制御する構造を採っていましたが、微細化が進むにつれ、チャネル幅の縮小による電気的制御の限界が見えてきました。こうした課題を打破するために登場したのが、GAA(Gate-All-Around)構造です。

GAAでは、チャネルをナノワイヤやナノシートの形状で形成し、それをゲート電極が上下左右の四方向すべてから包み込む構造となっています。これにより、チャネル電流のオン・オフ制御がより精密になり、リーク電流の抑制やスイッチング性能の向上が実現します。チャネルの寸法や層構造を調整することで特性を柔軟に最適化できる点も、GAAの大きな利点です。

2022年、韓国のSamsung Electronicsは3nm世代の量産プロセスにおいて、GAA技術を世界で初めて本格採用しました。同社が採用した「ナノシートGAA構造」では、複数のナノシートを積層し、デバイスのドライブ電流を向上させると同時に、設計の自由度を確保しています。

今後、GAAはFinFETに代わる新たな主流技術として、2nm以降のプロセスにおける中心的な構造になると見込まれており、製造装置や材料面でも技術革新が加速しています。

次世代技術として注目のCFET

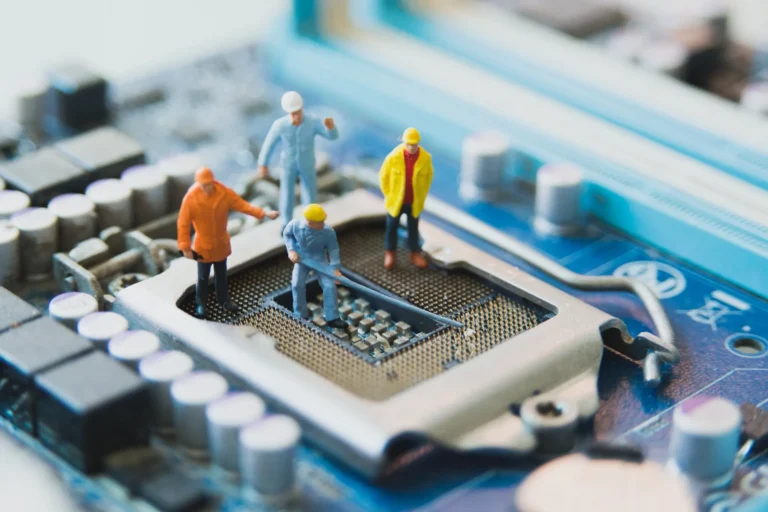

GAA構造の限界を見据え、さらなる集積度と性能向上を目指して注目されているのが、CFET(Complementary FET)と呼ばれる次世代トランジスタ構造です。CFETでは、通常は平面上に並べられていたpMOSとnMOSを、同一の垂直軸上に縦方向に積層することで、デバイスの面積を大幅に削減し、レイアウト効率を極限まで高めることが可能になります。

この構造により、従来のFinFETやGAAでは避けられなかったトランジスタ間の水平スペースを不要とし、チップ全体のスケーリングをさらに一段進めることができます。また、pMOSとnMOSを積層することで、信号の遅延時間や消費電力のバランス調整もしやすくなり、高速動作と低電力化の両立が期待されます。

CFETの実現には、極めて高精度な3次元構造制御や、プロセスばらつきの抑制、高アスペクト比での堆積・エッチング技術の確立が必要不可欠です。そのため、現在は研究開発段階にあり、IntelやTSMC、Samsungをはじめとする主要半導体メーカーが次世代製造技術の柱として開発を進めています。

商用化の時期については明確ではありませんが、2nm世代以降での導入が有力視されており、ポストGAAの有望技術として半導体業界の注目を集めています。

まとめ

微細化が限界に近づく中、FinFETやGAAといった新しいトランジスタ構造は、短チャネル効果への対策として不可欠な技術となりました。FinFETは立体構造によって制御性と性能を高め、GAAはチャネルを全方向から囲うことでさらに精密な電流制御を可能にしました。

今後は、pMOSとnMOSを積層するCFET構造が主流となる可能性もあり、半導体技術は構造革新を中心に進化を続けています。これらの技術動向は、ロジック半導体の高性能化と低消費電力化を同時に実現する鍵となっており、製造現場における設計戦略にも大きな影響を与えています。